Research Log/Tracing

Offcore Response Event

ycchae

2022. 3. 6. 19:03

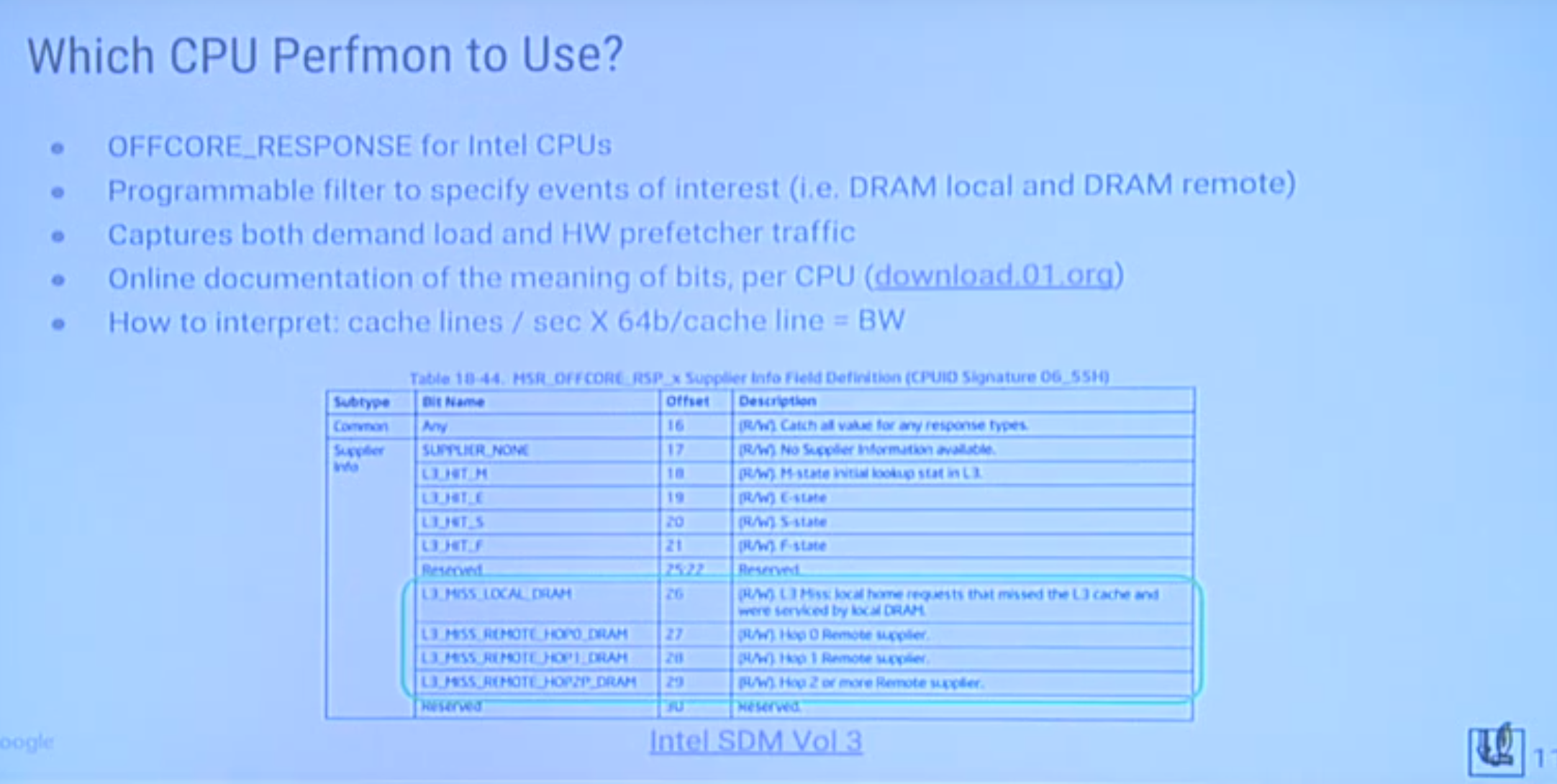

Event number 0B7H support offcore response monitoring using an associated configuration MSR, MSR_OFFCORE_RSP0 (address 1A6H) in conjunction with umask value 01H or MSR_OFFCORE_RSP1 (address 1A7H) in conjunction with umask value 02H. Table 18-14 lists the event code, mask value and additional off-core configuration MSR that must be programmed to count off-core response events using IA32_PMCx.

The layout of MSR_OFFCORE_RSP0 and MSR_OFFCORE_RSP1 are shown in Figure 18-18 and Figure 18-19.

VS

| MEM_LOAD_UOPS_L3_MISS_RETIRED.LOCAL_DRAM | This event counts retired load uops where the data came from local DRAM. This does not include hardware prefetches. |